项目挑战

SysML仿真结构转化

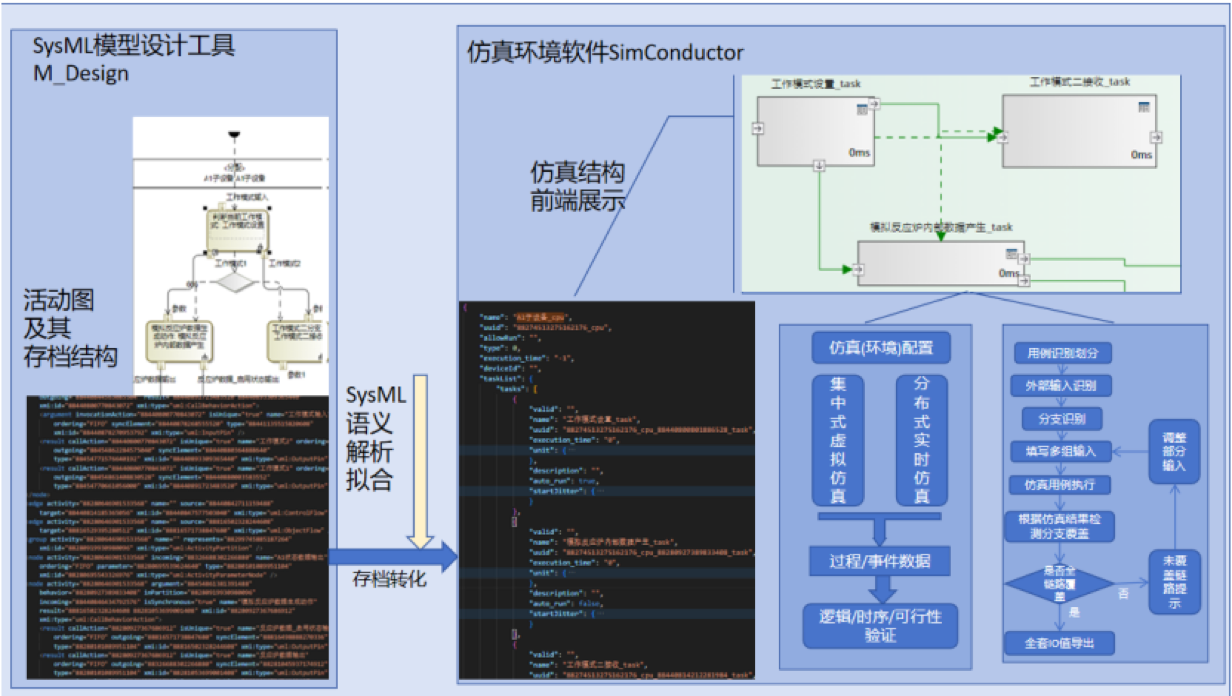

对SysML设计模型进行识别转化为Simconductor仿真模型,不仅要实现数据壁垒的打破,更要实现对SysML语义的解析完成对设计业务的复现。

仿真总线设计适配

原生SysML缺乏对仿真元素的适配——尤其涉及半实物仿真的通信总线映射相关,设计和仿真两端都需要不断开发和验证打磨来完成桥接。

“测试用例”工具实现

针对甲方拟定的“系统 - 功能用例 - 分系统 - 设备 - 软件”数字模型结构,需根据用例划分并识别不同层级的链路分支以及执行识别。

DDS通信集成

出于甲方产品使用DDS进行通信,为实现设计模型能转化后与甲方实物产品进行仿真闭合,Simconductor需实现对异构通信方式的集成。